Data Flow Modelling in Verilog

Ansys simulation helps model the behavior of fluid flow as aircraft travel above hypersonic speed including strong shocks plasma and structural deformation. GDT defines degree of accuracy and precision required on controlled feature of part.

Outline Introduction Basics Of The Verilog Language Ppt Download

Understanding the structures that underlie the programs algorithms and languages used in data science and elsewhere.

. A comprehensive resource on Verilog HDL for beginners and experts large and complicated digital circuits can be incorporated into hardware by using Verilog a hardware description language HDL. We refer to a multiplexer with the terms MUX and MPX. Further dividing the 4-bit adder into 1-bit adder.

Mastery of a particular programming language while. We would again start by declaring the module. Xilinx Runtime XRT is implemented as a combination of user-space and kernel driver components.

To understand this lets take an example of designing a 16-bit adder as shown in the figure below. GDT is very important part of mechanical product design. If you are interested in algorithms performance engineering data capture and analysis trading infrastructure or exchange gateways youll love Akunacademy.

QUANT Quant internships expose you to the financial markets where youll gain experience on anything from identifying and defining significant algorithm improvements our trading strategies pricing models execution logic and. Ansys Photonics Verilog-A. External tools add Ada C PHP5 Ruby shapefile C SQL Sybase Postgres Oracle DB2 MS-SQL MySQL No No Uses Python as scripting language.

Assign Y A. Expands computational concepts and techniques of abstraction. AEDT provides access to the Ansys gold-standard electromagnetics simulation solutions such as Ansys HFSS Ansys Maxwell Ansys Q3D Extractor Ansys SIwave and Ansys Icepak using electrical CAD ECAD and mechanical CAD MCAD.

The concurrent statements in VHDL are WHEN and GENERATE. Besides them assignments using only operators AND NOT sll etc can also be used to construct code. Fall 2022 Development of Computer Science topics appearing in Foundations of Data Science C8.

Ansys Electronics Desktop AEDT The Ansys Electronics Desktop AEDT is a platform that enables true electronics system design. Ansys fluid mixing simulation tools help you to model the mixing process and blending of one or more fluid-like materials. A multiplexer is a device that selects one output from multiple inputs.

Module AND_2_data_flow output Y input A B. We can design the given task into the design flow processs domain Behavioral Structural and Geometrical. Verilog Tutorial Lexical Tokens ASIC Design Flow Design Abstraction Layers Verilog Data Types Behavioral Modelling Timing Verilog Module RTL Verilog Scalar Vector Verilog Arrays Verilog Port Assign Statements Verilog Operators Verilog always Block Verilog Initial block Verilog Block Statements Verilog Assignment Blocking Non-blocking.

Partly No No No Included Python script codegenpy export filter to Python C JavaScript Pascal Java PHP. What is meant by GDT. Then we use assignment statements in data flow modeling.

Supports use case diagrams auto-generated flow diagrams screen mock-ups and free-form diagrams. XRT supports Alveo PCIe -based cards as well as Versal and Zynq UltraScale MPSoC-based embedded system platforms and provides a software interface to Xilinx programmable logic devices. Geometric Dimension Tolerance GDT is a system for defining engineering tolerances.

Here the whole chip of 16 bit adder is divided into four modules of 4-bit adders. Multiplexers are used in communication systems to increase the amount of data sent over a network within a certain amount of time and bandwidth. A designer aspiring to master this versatile language must first become familiar with its constructs practice their use in real applications and.

In this modeling style the flow of data through the entity is expressed using concurrent parallel signal. It is also known as a data selector. Endmodule Just like the and operation the logical operator performs a binary multiplication of the inputs we write.

Verilog code for AND gate using data-flow modeling.

Verilog Code For 4x1 Mux With Testbench Youtube

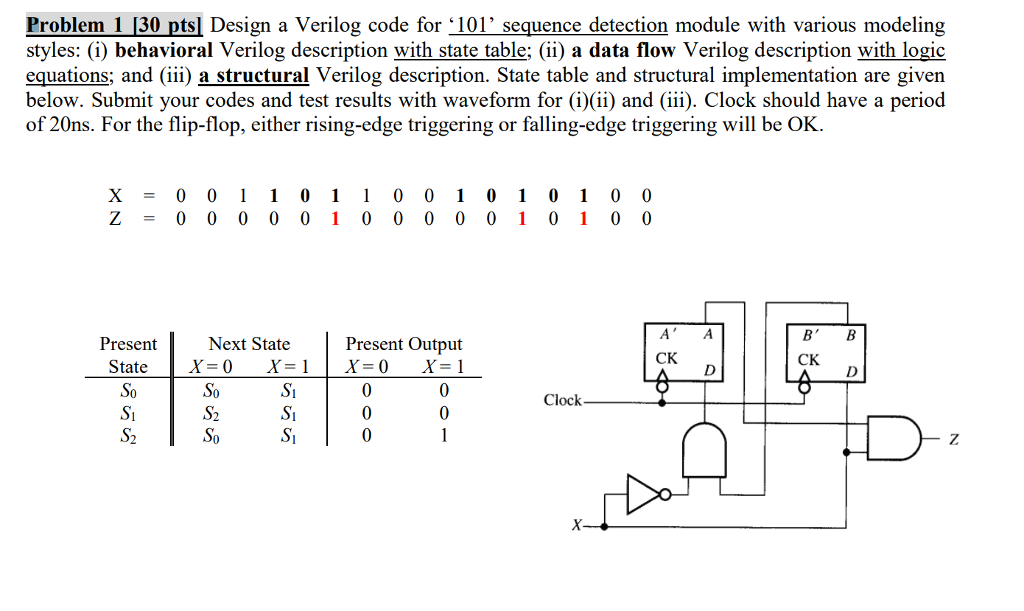

Solved Problem 1 130 Pts Design A Verilog Code For 101 Chegg Com

Outline Introduction Basics Of The Verilog Language Gate Level Modeling Data Flow Modeling Behavioral Modeling Task And Function Ppt Download

No comments for "Data Flow Modelling in Verilog"

Post a Comment